Разделы сайта

- Главная

- Исследования и анализ современных технологий

- IP-телефония

- Антенно-фидерные устройства

- Виртуальное построение рабочей локальной сети

- Влияние электромагнитного поля на подземную проволочную антенну

- Микрополосковая антенная решетка

- Система экологического мониторинга вредных газовых выбросов

- Организация процесса производства цифрового телевиденья

Модернизация канала формирования импульсов запуска блока Т-17М

Единичный сигнал подается на 64 вход шифратора, возбуждая на его выходе код, соответствующий числу 64. Этот код записывается в семиразрядный счетчик при наличии логической единицы на входе разрешения записи, поступающей с нулевого выхода дешифратора.

На счетный вход семиразрядного счетчика поступают импульсы частотой 300 кГц с формирователя эталонного напряжения. Код, записанный в семиразрядном счетчике, поступает на дешифратор, последовательно возбуждая его выходы. При возбуждении 125 выхода формируется импульс запуска I, который используется для выработки остальных синхронизирующих импульсов. Частота формирования этого импульса соответствует 4750 Гц. Далее импульс запуска I подается в аппаратуру опознавания.

Импульсом с 127 выхода дешифратора производится сброс семиразрядного счетчика в исходное нулевое состояние.

Таким образом, в штатном режиме схема формирует импульс запуска I с постоянной частотой повторения 4750 Гц, что соответствует набору в семиразрядный счетчик чисел от 64 до 125.

Функционирование разработанного устройства в режиме вобуляции частоты.

Смысл данного режима состоит в формировании импульса запуска I переменной частотой повторения от 3650 до 4750 Гц.

В данном режиме в работе принимают участие все элементы схемы.

При поступлении сигнала "+5 В Вобуляция" на S вход RS-триггера он переводится в одно из устойчивых состояний и с его выхода снимается положительный сигнал, соответствующий логической 1 (на R вход через инвертор подается сигнал логического 0). С поступлением сформированного импульса запуска I в предыдущем периоде повторения с выхода схемы И снимается сигнал логической единицы, который поступает на информационный вход демультиплексора D, подключающий один из счетных входов реверсивного счетчика. В исходном состоянии в счетчик записан нулевой код, поэтому с выхода Р - снимается логическая единица. С использованием коммутатора, состоящего из RS-триггера, элемента И и двух инверторов на адресный вход демультиплексора подается логическая единица, переключающая реверсивный счетчик в режим сложения. Сброс счетчика в режиме вобуляции не производится, так как на вход R подается сигнал логического 0 с R входа RS-триггера. Таким образом, в реверсивный счетчик записывается двоичный код, соответствующий числу 1. При этом возбуждается 1 выход дешифратора, с которого сигнал логической единицы подается на 65 вход шифратора, формирующего двоичный код числа 65 на параллельных входах семиразрядного счетчика. Таким образом, начало счета семиразрядного счетчика по импульсам частотой 300 кГц соответствует числу 65. При достижении в счетчике двоичного кода числа 125 формируется импульс запуска I, который через элемент И поступает на информационный вход демультиплексора D, записывая в реверсивный счетчик двоичный код числа 2. При этом семиразрядный счетчик начнет чет с двоичного кода числа 66. Так будет продолжаться до тех пор, пока не произойдет заполнение всех разрядов реверсивного счетчика, в который будет записано число 15, а семиразрядный счетчик начнет счет по импульсам частотой 300 кГц с двоичного кода числа 79. При заполнении разрядов реверсивного счетчика на выходе Р+ появляется сигнал логической единицы, который с помощью коммутатора, состоящего из RS-триггера, элемента И и двух инверторов, на адресный вход демультиплексора подается сигнал логического 0, переключающий реверсивный счетчик в режим вычитания. При этом каждый сформированный импульс запуска I записывает на параллельные входы семиразрядного счетчика двоичные коды чисел от 79 до 64.

Таким образом, работа схемы обеспечивает формирование импульса запуска I с переменной частотой повторения от 3650 до 4750 Гц.

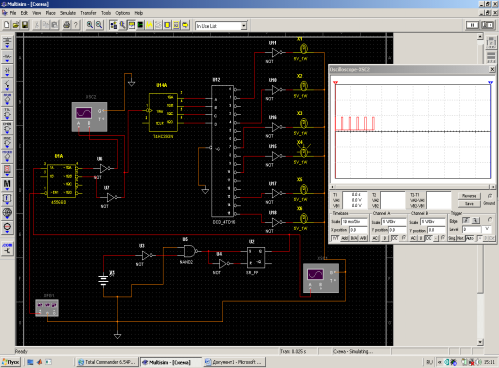

Для исследования работоспособности разработанного устройства использована система схемотехнического моделирования Electronics Workbench Multisim, которая показала возможность технической реализации разработанного устройства для формирования импульса запуска I (рисунок 2.4).

Рисунок 2.4 - Внешний вид окна программы Electronics Workbench Multisim

Выводы:

Для технической реализации системы синхронизации разработана ее структурная схема, которая содержит формирователи импульсов запуска I, импульсов запуска II, импульсов запуска передатчика, ЧПК, ТРУ, строб-импульсов. В качестве опорного напряжения используется сигнал формирователя эталонного напряжения 300 кГц. Таким образом, предложенная структура соответствует логике работы существующих систем СДЦ и измерения дальности при формировании синхронизирующих импульсов: формирование импульса запуска I - формирование импульса запуска II - формирование импульса запуска ЧПК, ТРУ и ПРД - формирование строб-импульсов.

Самое читаемое:

Операционный микроэлектронный усилитель

Современная радиоэлектронная аппаратура (РЭА) характеризуется

тремя основными чертами:

резким возрастанием количества компонентов и в связи с этим

значительным уплотнением аппаратуры;

мобильностью, так как РЭА устанавливается на объектах, движущихся

с космическими скоростями;

количественным ростом выпуска аппаратуры и, след ...