Разделы сайта

- Главная

- Исследования и анализ современных технологий

- IP-телефония

- Антенно-фидерные устройства

- Виртуальное построение рабочей локальной сети

- Влияние электромагнитного поля на подземную проволочную антенну

- Микрополосковая антенная решетка

- Система экологического мониторинга вредных газовых выбросов

- Организация процесса производства цифрового телевиденья

Разработка принципиальной схемы контроллера

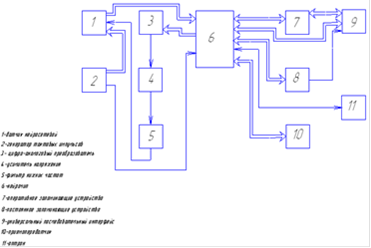

Рисунок 4.3.1 Структурная схема, разрабатываемой системы

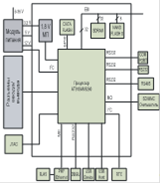

Рассмотрим общую схему ПАК, в которой показаны все основные блоки и протоколы передачи информации между ними. Эта схема представлена на рисунке 4.3.2.

Рисунок 4.3.2. Функциональная схема ПАК

Процессор предназначен для выполнения вычислений и управления интерфейсами ПАК и управляется микропрограммой, заложенной в восьмибитной DATA FLASH. ОЗУ данной операционной части группового контроллера выполняет вспомогательную функцию хранения промежуточных данных, полученных в процессе обработки информации процессором. Nand Flash выполняет функцию долговременного хранения данных.

Так как процессор обладает большими функциональными возможностями, то решено добавить в схему ПАК несколько периферийных устройств помимо заявленных в техническом задании.

Также в плату ПАК интегрирован IDE интерфейс подключенный на шину EBI.

Данная архитектура ПАК позволяет реализовать большинство возможностей процессора. Это является большим плюсом и позволяет отлаживать большой перечень различных программ самых разнообразных назначений.

Следует заметить, что для осуществления подобной функциональности необходимо подобрать современную элементную базу. И в полной мере может обеспечиваться современными микропроцессорами с RISC архитектурой, имеющими не только достаточный функционал, но и производительность, позволяющие выполнять современные программные инструменты и при этом обладают очень малым энергопотреблением.

Самое читаемое:

Автоматизация технологических процессов в условиях технологического комплекса КК-АДСК-МНЛЗ ПАО МК Азовсталь, г. Мариуполь

Автоматизация управления технологическими процессами и

производством играет важную роль в непрерывном увеличении выпуска продукции в

нашей стране. Интенсификация и усложнение технологических процессов, рост

единичной мощности агрегатов и повышение требований к качеству готовой

продукции в соответствии с международными стандартами де ...