Разделы сайта

- Главная

- Исследования и анализ современных технологий

- IP-телефония

- Антенно-фидерные устройства

- Виртуальное построение рабочей локальной сети

- Влияние электромагнитного поля на подземную проволочную антенну

- Микрополосковая антенная решетка

- Система экологического мониторинга вредных газовых выбросов

- Организация процесса производства цифрового телевиденья

Логическая структура микропроцессорной системы на основе комплекта БИС секционного микропроцессора

Комплект БИС секционного микропроцессора

Вследствие малой разрядности секций микропроцессора и определенности функционального наполнения их реализуют, как правило, в виде биполярных БИС в корпусе с 42 - 64 выводами. Большое количество выводов корпуса одной секции БИС и внутренняя логическая структура секции микропроцессора обеспечивают построение микро-ЭВМ различной разрядности с наращиваемым числом входов прерываний, различным количеством подключаемых УВВ и т.д.

В состав комплекта БИС секционного микропроцессора входит значительное число секций. Рассмотрим наиболее важные из них.

Секции арифметическо-логических БИС используются для построения операционных блоков обработки информации. Они включают в себя несколько разрядов АЛБ, управляющих регистров, СОЗУ и узлов связи с информационными магистралями. Секции БИС опережающего параллельного переноса позволяют объединить арифметическо-логические секции в высокоскоростные блоки обработки информации за счет создания пирамидальных схем ускоренного переноса.

Секции БИС для задания последовательности микрокоманд, применяемые для построения блоков микропрограммного управления, дают возможность вырабатывать выходной код в зависимости от внешнего управляющего кода, кода состояния процессора, содержимого внутреннего стека, а также внутреннего состояния самой секции.

При микропрограммном управлении каждой команде соответствует микропрограмма - последовательность микрокоманд, выполнение которых приводит к выполнению операций, заданных командой. Микрокоманда управляет выполнением одной или нескольких микроопераций.

БИС микропрограммного управления на основе программируемой логической матрицы (ПЛМ)

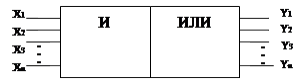

Рис.8 Структура программируемой матрицы

Схема ПЛМ приведена на рис.8, она содержит логические матрицы адресов И и данных ИЛИ, с помощью которых осуществляется преобразование входного n-разрядного кода в m-разрядный выходной код. Матрицы данных ПЗУ и ПЛМ совпадают. Различие ПЗУ и ПЛМ существует только между матрицами адресов или дешифраторами адресов.

При построении дешифратора адресов ПЗУ обязательна постановка коммутирующих элементов между входными шинами и шинами переходных функций. Поэтому в дешифраторе каждой комбинации входных сигналов соответствует одна и только одна переходная функция. Всего переходных функций ![]() . В ПЛМ коммутирующие элементы для ряда входных переменных могут отсутствовать. Поэтому некоторые переменные не влияют на выбор переходной функции. Число переходных функций ПЛМ

. В ПЛМ коммутирующие элементы для ряда входных переменных могут отсутствовать. Поэтому некоторые переменные не влияют на выбор переходной функции. Число переходных функций ПЛМ ![]() .

.

На практике получили распространение ПЛМ с многоразрядными адресами, для которых число входных переменных равно 16.24 разрядам и более. ПЗУ и ПЛМ различаются по системе адресации информационного поля данных, распределению информационных полей, возможности одновременного опроса нескольких переходных функций. Так как в ПЛМ осуществляется избыточная свободная адресация, а в ПЗУ - жесткая не избыточная адресация, то в ПЛМ большому количеству входных комбинаций адресов соответствует малое количество адресуемых переходных функций. Разные адреса могут определять одну и ту же переходную функцию или не определять ни одной. Кроме того, возможны варианты, когда один адрес определяет более одной переходной функции.

Специфика внутреннего распределения информационных полей в ПЛМ заключается в том, что посредством двух (или более) различных адресов можно адресовать одну и ту же область данных матрицы, что позволяет обращаться к микропрограммам по различным адресам. Следовательно, появляется возможность микропрограммного перехода к микропрограммам из различных текущих условий без выполнения специальных микрокоманд перехода. Эта особенность адресации обеспечивается наличием безразличных разрядов в коде адреса.

Одновременность выбора двух (и более) выходных информационных слов и объединение их по ИЛИ на выходе ПЛМ определяются возможностью адресации различных переходных функций одним адресом. При этом сохраняется выбор каждого информационного слова своим специфичным адресом. Жесткая не избыточная адресация ПЗУ позволяет иметь однозначное соответствие адресов и слов в информационном поле данных.

Самое читаемое:

Имитационное моделирование сети Ethernet в среде GPSS World

Развитие моделирования сетей и систем телекоммуникации непосредственно

связано с внедрение новых телекоммуникационных и информационных технологий. Это

связано с тем, что моделирование является основным современным методом

исследования телекоммуникационных систем.

Целью курсовой работы является овладение методами моделировани ...