Разделы сайта

- Главная

- Исследования и анализ современных технологий

- IP-телефония

- Антенно-фидерные устройства

- Виртуальное построение рабочей локальной сети

- Влияние электромагнитного поля на подземную проволочную антенну

- Микрополосковая антенная решетка

- Система экологического мониторинга вредных газовых выбросов

- Организация процесса производства цифрового телевиденья

Радиорелейные линии синхронной цифровой иерархии

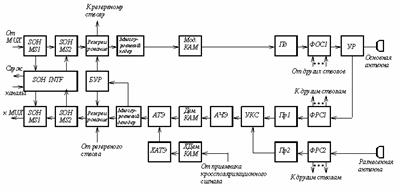

Рисунок 2.3.2 - структурная схема оконечной радиорелейной станции

На вход рабочего ствола РРЛ СЦИ по кабельной соединительной линии от MUX поступает линейный цифровой сигнал в коде CMI со скоростью 155.52 Мбит/с (STM-1).

На ОРС1 заканчивается мультиплексная секция кабельной соединительной линии, на ней производится обработка заголовка этой секции (модуль SOH MS1) рисунок 2.3.2 и 2.3.3. В этом модуле (C/N-преобразователь) осуществляется преобразование линейного кода CMI в код NRZ, который и используется в аппаратуре радиорелейных станций как наиболее узкополосный из двоичных кодов.

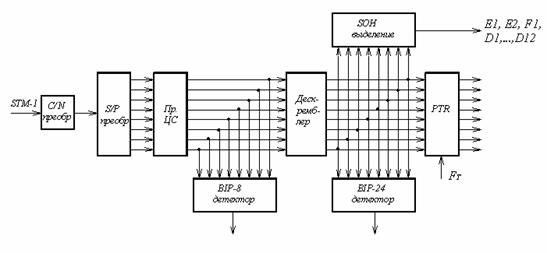

Рисунок 2.3.3 - Структурная схема обработки секционного заголовка на приемной стороне

Здесь же осуществляется преобразование входного цифрового потока 155.52 Мбит/с в восемь параллельных потоков по 19.44 Мбит/с (S/P-преобразователь), для того чтобы в дальнейшем можно было использовать микросхемотехнику с невысоким быстродействием, но при этом количество комплектов оборудования увеличивается в восемь раз. Для обеспечения этих преобразований (C/N и S/P) необходимо тактовая частота, которая выделяется из входного сигнала.

Обработка секционного заголовка заключается в выделении и соответствующей обработке байт секционного заголовка. Для определения местоположения байт заголовка в структуре синхронного транспортного модуля определяется начало его цикла, то есть осуществляется синхронизация начала цикла генераторного оборудования (ГО) приема под начало цикла принимаемого сигнала. Для этого используется приемник циклового синхросигнала (Пр.ЦС).

Контроль ошибочно принятых бит производится по коду BIP-8 (BIP-8 детектор), для чего рассчитываются битовые суммы по всем байтам текущего цикла и сравниваются с битовыми суммами, записанными на передающем конце в байт B1 следующего цикла.

Далее сигнал обрабатывается в дескремблере, где из него удаляется псевдослучайная последовательность (ПСП), введенная на передающей стороне в скремблере для того, чтобы исключить появление в передаваемом цифровом сигнале длинных последовательностей «0» и «1». Наличие таких последовательностей приводит к отсутствию в такие моменты времени информации о тактовой частоте, что ухудшает работу выделителя тактовой частоты.

Затем производится контроль ошибок по коду BIP-24 (BIP-24 детектор), для чего рассчитываются 24 битовые суммы по всем тройкам байт (кроме байт заголовка регенерационной секции RSOH) текущего цикла и сравниваются с битовыми суммами записанными на передающем конце в байты В2 следующего цикла. Здесь же производится выделение байт заголовка (SOH выделение), используемых для организации служебных каналов: Е1, Е2, F1 - каналы служебной связи на мультиплексных и регенерационных секциях; D1,…D12 - каналы для системы телеуправления. С выхода модуля SOH выделенные сигналы поступают на интерфейс секционного заголовка (SOH INTF) (рисунок 2.3.2), от куда подаются на соответствующее оборудование или проходят транзитом.

С выхода дескремблера цифровой сигнал восьмью потоками поступает на модуль обработки AU-указателя (PTR), где устраняется расхождение фаз между значением AU-указателя и местоположением первого байта нагрузки, появившееся при прохождении сигнала через мультиплексную секцию и перезаписи цифровых потоков под тактовую частоту местного генератора (reference clock). При этом изменяется значение AU-указателя.

Самое читаемое:

Локальные системы автоматики

1). Закон регулирования - ПИД; критерий качества регулирования 20%

перерегулирования (=20%).

Рис. 1. Кривая разгона.

Аппроксимация кривой разгона апериодическим звеном первого порядка с

запаздыванием. Определение соотношения наклона угла (0.1 - 0.2).

Рис. 2.

Рассмотрим кривую разгона (рис. 1) с с ...