Разделы сайта

- Главная

- Исследования и анализ современных технологий

- IP-телефония

- Антенно-фидерные устройства

- Виртуальное построение рабочей локальной сети

- Влияние электромагнитного поля на подземную проволочную антенну

- Микрополосковая антенная решетка

- Система экологического мониторинга вредных газовых выбросов

- Организация процесса производства цифрового телевиденья

Радиорелейные линии синхронной цифровой иерархии

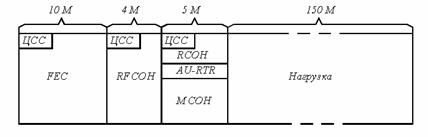

Рисунок 2.3.5 - Структура сигнала на выходе многоуровневого кодера

После мультиплексора сигналы поступают на скремблер, в котором к ним добавляется псевдослучайная последовательность, устраняющая в двоичном сигнале длинные последовательности нулей и единиц.

В преобразователе скорости 2 суммарная скорость цифрового потока увеличивается на 10 Мбит/с (рисунок 2.3.5) и полученные цифровых потоков суммарной скоростью около 170 Мбит/с поступают на модуль предкоррекции ошибок и размещения. Свободные тактовые интервалы, полученные на выходе преобразователя скорости 2, присутствуют только в первом в соотношении 3/4 (три информационных символа из четырех) и втором в соотношении 11/12 цифровых потоков из шести.

Операция размещения (mapping) полученных цифровых потоков на фазоамплитудной плоскости (constellation - созвездие) сигнала модулятора заключается в том, что соседние точки на созвездии определяются первыми из шести потоков, который имеет наибольшую защиту (3/4). Это определяется тем, что из-за действия шумов и помех наиболее вероятным будет переход данной точки созвездия на соседние точки.

Самое читаемое:

Микрофон устройство, принцип действия, применение

Для обработки и передачи на расстояния звуковой и визуальной

информации звук и оптическое изображение необходимо представить в форме

электрических сигналов.

Звук преобразуют в электрический сигнал посредством аппаратов,

названных микрофоном. Микрофон это устройство для преобразования и усиления

звуковых частот.

Микрофон решает ...